حل تشریحی سوالات الکترونیک دیجیتال - کنکور ارشد مهندسی کامپیوتر 1404

منوی آزمون (درس ها)

سوالات الکترونیک دیجیتال

6 سوالدر یک وارون گر CMOS، نسبت تقریبی را چه مقدار تعیین کنیم تا به ازای ولتاژ ورودی 1/5 ولت، جریان ایستا (اتصال کوتاه) حداکثر شود؟

0/5

1/0

1/4

2/9

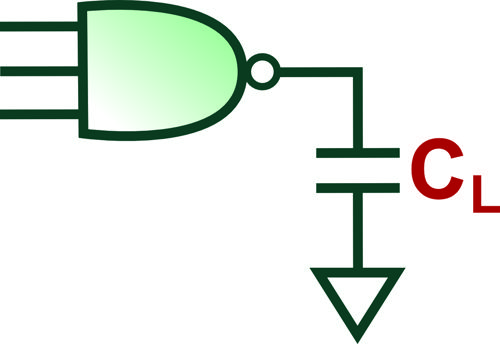

اگر W همه ترانزیستورهای گیت NAND سه ورودی نمایش داده شده دو برابر شود، بیشترین تأخیر بالارونده خروجی این گیت، طبق مدل المور چگونه تغییر می کند؟ (فرض کنید نشان دهنده خازن ناشی از ورودی گیت های طبقه بعد باشد که ابعاد ترانزیستورهای آن ثابت باقی می ماند.)

بسته به ابعاد اولیه ترانزیستورها، ممکن است تأخیر از نصف مقدار اولیه بزرگ تر یا کوچک تر شود.

تأخیر کاهش می یابد، اما از نصف تأخیر اولیه بزرگ تر خواهد بود.

تأخیر کاهش می یابد و از نصف تأخیر اولیه کوچکتر خواهد بود.

تأخیر تغییری نمی کند.

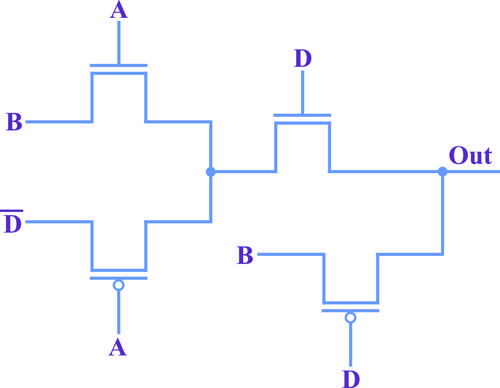

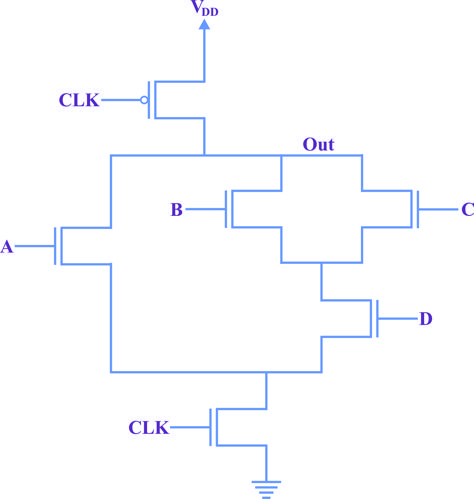

ساختار ترانزیستوری زیر، چه تابع منطقی را پیاده سازی می کند؟

فرض کنید ورودی های A و به صورت شکل زیر تغییر کنند. ولتاژ نهایی گروه out چه مقداری می شود؟ (فرض کنید ولتاژ آستانه تمامی ترانزیستورهای NMOS ، برابر و ولتاژ آستانه تمامی ترانزیستورهای PMOS ، برابر باشد.

صفر

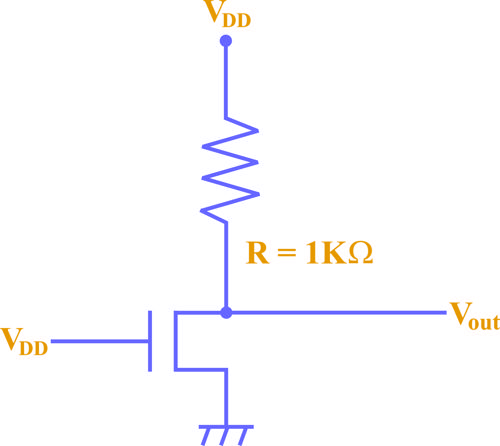

در وارون گر NMOS شکل زیر، مقدار تقریبی ترانزیستور چقدر باید باشد تا خروجی برابر شود؟

3.2

5.3

6.4

10.7

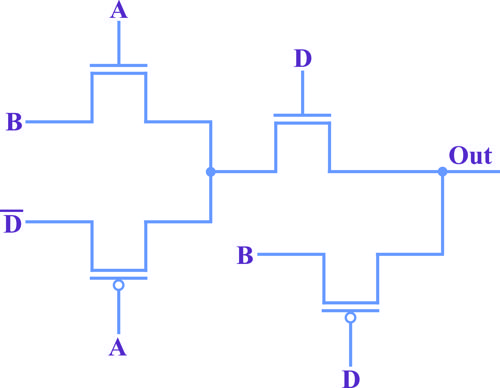

اعمال کدام یک از ورودی های زیر می تواند منجر به افت ناخواسته ولتاژ خروجی (ولتاژ out) ناشی از انتشار بار در فاز ارزیابی (Evaluate) شود؟ (فرض کنید ورودی ها در لبه بالارونده کلاک تغییر می کنند.)

(0,1,1,0)

(0,0,0,1)

(1,1,0,0)

تفاوتی بین موارد فوق وجود ندارد.