حل تشریحی سوالات معماری کامپیوتر - کنکور ارشد مهندسی کامپیوتر 1400

منوی آزمون (درس ها)

سوالات معماری کامپیوتر

7 سوالعدد مکمل2 10011101 در عملیات ضرب به روش Booth به عنوان ضرب کننده (Multiplier) شرکت میکند. این عدد بر اساس این روش با توجه به ارقام () به چه صورت رمزگشایی میشود؟

یک سیستم حافظهای دارای یک حافظه اصلی به گنجایش 4GW و یک حافظه Cache با گنجایش 256kW (4 کلمه در هر بلوک) است.

(4 کلمه در هر بلوک) است.

اگر Cache از مکانیزم way set associative استفاده کند، کدام گزینه تعداد بیت های لازم برای فیلدهای Tag و Index را نشان میدهد؟

14 بیت برای Index و 14 بیت برای Tag

14 بیت برای Index و 16 بیت برای Tag

16 بیت برای Index و 14 بیت برای Tag

16 بیت برای Index و 16 بیت برای Tag

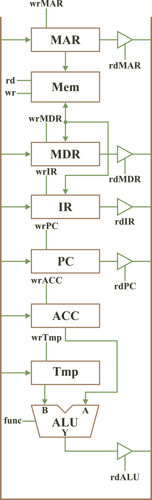

شکل زیر مسیر داده یک پردازنده Accumulator Based ساده و جدول صحت واحد ALU ان را نشان میدهد. برای اجرای دستور TWOSCOMP adr به چند سیکل نیاز است؟ (این دستور محتویات خانه حافظه به ادرس adr را مکمل 2 میکند. توجه کنید که باید از مرحله واکشی دستور کار را شروع کنید.)

Y | Fune |

|---|---|

A | 000 |

B | 001 |

A+B | 010 |

A-B | 011 |

B+1 | 100 |

A+1 | 101 |

A and B | 110 |

NOT B | 111 |

5

6

9

10

قالب نمایش اعداد ممیز شناور زیر را در نظر بگیرید . درصورتی که در این نمایش از Implicit One Representation و Biased-4 اسنفاده شود، کدام گزینه، بزرگترین عدد قابل نمایش را نشان میدهد؟

7/5

15/5

120

248

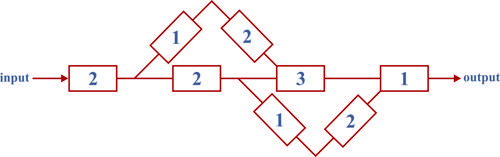

در مدار زیر با توجه به تاخیر هر ماژول که در ان ذکر شده است، در صورت استفاده از خط لوله در بهترین حالت، برای بینهایت ورودی مختلف حداکثر تسریع کدام است؟ (تاخیر اتصالات ناچیز است)

3

4

8

9

کدام گزاره نادرست است؟

هنگام تقسیم مقسوم 2n بیتی بر مقسوم علیه n بیتی در خارج قسمت n بیتی شرط کافی سریز نشدن ان است که مقسوم علیه بزرگتر از نیمه پر ارزش مقسوم باشد.

هنگام تقسیم مقسوم 3n بیتی بر مقسوم علیه 2n بیتی و خارج قسمت n بیتی شرط کافی سریز نشدن ان است که مقسوم علیه بزرگتر از 2n بیت پر ارزش مقسوم باشد.

هنگام تقسیم مقسوم 4n بیتی بر مقسوم علیه n بیتی و خارج قسمت 3n بیتی شرط کافی سریز نشدن ان است که مقسوم علیه از n بیت پر ارزش مقسوم بزرگتر باشد.

هنگام تقسیم مقسوم 4n بیتی بر مقسوم علیه 3n بیتی در خارج قسمت n بیتی شرط کافی سریز نشدن ان است که 2n بیت پرارزش مقسوم از نیمه پرارزش مقسوم علیه کوچکتر باشد.

در یک سیستم دیجیتال پردازش ورودی 12 نانوثانیه زمان میبرد. دو خط لوله مختلف A با 6 طبقه و تاخیر طبقات (1,2,2,3,2,1) نانوثانیهو خط لوله B با 4 طبقه و تاخیر طبقات (3,3,4,3) برای این سیستم طراحی و ساخته شده اند. (تاخیر بافر بین طبقات ناچیز است) . اگر زمان پردازش n ورودی با خط لوله A را با و زمان پردازش n ورودی با خط لوله B را با نشان دهیم، کدام مورد درست است؟