حل تشریحی سوالات مدار منطقی و معماری کامپیوتر - کنکور دکتری مهندسی کامپیوتر 1403

سوالات مدار منطقی و معماری کامپیوتر

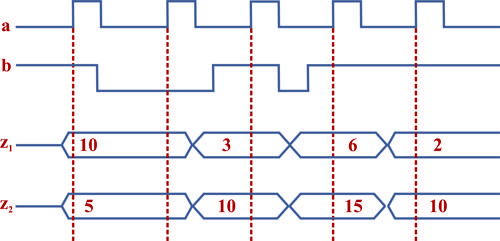

20 سوالکد Verilog/VHDL زیر را در نظر بگیرید. با توجه به مقادیر ورودیها که بهصورت شکل موج داده شدهاند، مقدار خروجی y پس از 5 سیکل، کدام مورد است؟

Verilog

module exam(z1,z2,a,b,y);

output y;

wire a,b;

reg[7:0]

always@(posedge a or negedge b)

if (!b)begin

y<=0;

end else begin

y<=y*z1+z2;

end

endmodule

VHDL

entity exam is

port(

a,b:in bit;

z1,z2: in signed (7downto 0);

y:out signed (8 downto 0));

end entity exam;

architecture AR of exam is

begin

process(a,b)

begin

if b='0' then

y<=(others=>'0');

elsif rising_edge(a)then

y<=<*z1+z2;

end if;

end process;

end AR;

40

150

160

با توجه به اینکه مقدار اولیه y در سیکل اول مشخص نیست، مقدار خروجی y نامشخص خواهد بود.

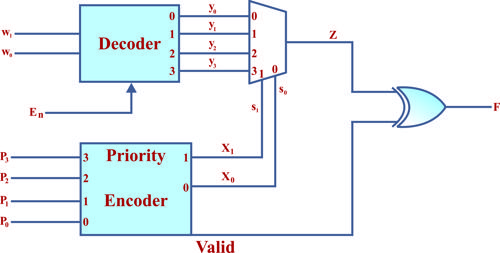

مقدار خروجی F بهازای دو حالت، حالت اول و حالت دوم ، به ترتیب، کدام است؟

صفر-صفر

صفر-یک

یک-صفر

یک-یک

در یک مدار ترتیبی با دو فلیپ نوع D، معادلات ورودیهای فلیپفلاپها و خروجی Y برحسب حالت جاری AB و ورودی X، بهصورت زیر است. در صورتی که در حالت AB=11، بهطور ناخواسته مقدار ذخیره شده در فلیپفلاپ B از یک به صفر تغییر کند، چه اتفاقی می افتد؟

مدار از این به بعد، بهطور کامل اشتباه کار میکند.

مدار به مدت دو سیکل، خروجی اشتباه میدهد و بعد از آن، درست کار میکند.

مدار فقط به مدت یک سیکل، خروجی اشتباه میدهد و بعد از آن، درست کار میکند.

مدار فقط به مدت سه سیکل، خروجی اشتباه میدهد و بعد از آن، درست کار میکند.

تعداد EPI های تابع زیر چند تا است؟

5

4

3

2

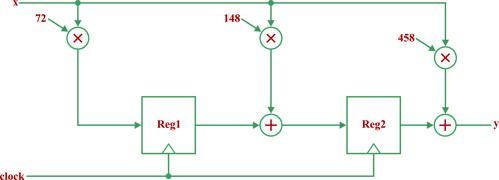

شکل زیر، مدار سطح انتقال ثبات (RTL) با ورودی x و خروجی y را نشان میدهد که ضرایب ثابت 148,72 و 458 در آن استفاده شدهاند. حداقل تعداد جمع کنندههای مورد نیاز جهت پیادهسازی این مدار بدون ضرب کننده، کدام است؟

7

4

5

6

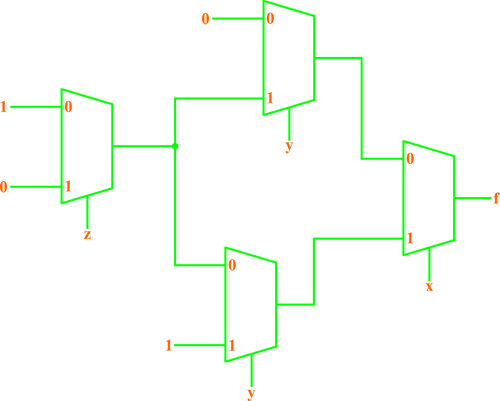

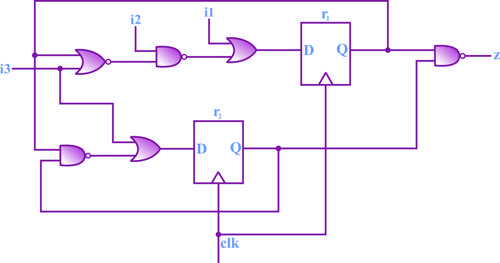

کدام مورد، تابع خروجی مدار زیر را نشان میدهد؟

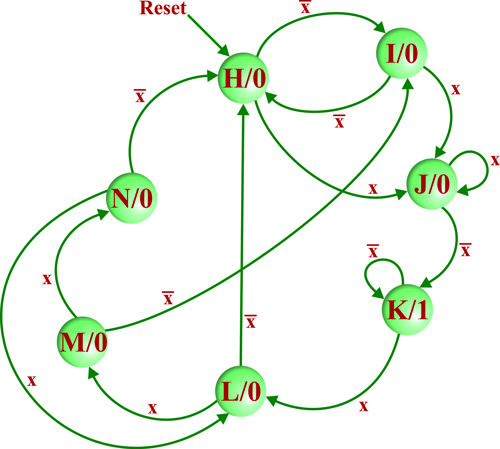

ماشین حالت زیر را در نظر بگیرید که شامل ورودی x و خروجی y به همراه هفت حالت میباشد. پس از بهینهسازی تعداد حالتها، کدام مورد، مدار سطح گیت معادل را توصیف میکند؟ (کدهای حالت را بهترتیب از حالت Reset بهصورت باینری در نظر بگیرید.)

دو فلیپفلاپ و با next stateهای متناظر و :

دو فلیپفلاپ و با next stateهای متناظر و :

دو فلیپفلاپ و با next stateهای متناظر و :

دو فلیپفلاپ و با next stateهای متناظر و :

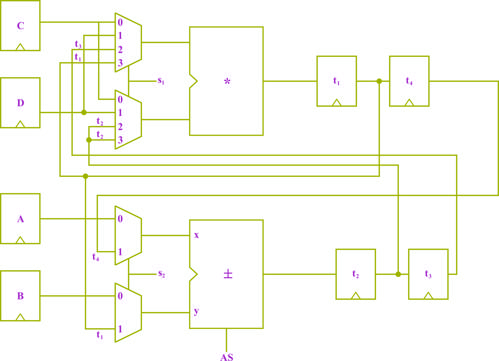

مسیر داده شکل زیر را در نظر بگیرید. سیگنالهای کنترلی مورد نیاز برای محاسبه ، کدام است؟

سیکل 1

سیکل 2

سیکل 3

سیکل 4

سیکل 1

سیکل 2

سیکل 3

سیکل 4

این مسیر داده، قادر به محاسبه مورد نظر نیست.

هر دو مورد 1 و 2

مدار ترتیبی زیر با ورودیهای الی و خروجی z را در نظر بگیرید. با توجه به اطلاعات زمانی داده شده، و چه مقادیری باید باشند تا مدار بتواند در فرکانس کار کند؟ (arrival time ورودیها، صفر لحاظ شوند.)

![]()

اهمیتی ندارد.

اهمیتی ندارد.

اهمیتی ندارد.

اهمیتی ندارد.

با فرض اینکه محدودیت ظرفیت ورودی (fanin) برای گیتها وجود نداشته باشد، تعداد گیتهای لازم برای پیاده سازی یک جمعکننده پیشبینی نقلی 5 بیتی (با در نظر گرفتن بیت نقلی خروجی رقم آخر)، چقدر است؟

(گیتهای موجود: AND، OR، NOT و XOR هستند، ولی گیتهای NOT در شمارش تعداد بهحساب نیامده اند.)

20

25

30

35

در ضرب دو عدد چهار بیتی به روش Array Multiplier، بهترتیب، به چند عدد تمام یا نیم جمعکننده (HA/FA) نیاز است و حداکثر تأخیر، چند HA/FA است؟

10 و 5

11 و 5

12 و 6

14 و 7

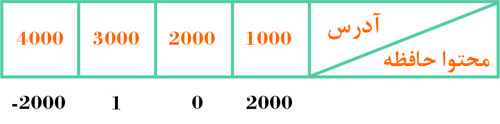

مقادیر موجود در حافظه، در آدرسهای مختلف نشان داده شده است. این مقادیر پس از اجرای این برنامه با فرض اینکه در ابتدا ثباتهای و باشد، چه خواهد بود؟ (با توجه: پردازنده مبتنی بر انباشتگر: Accumulator است و علامت یعنی مراجعه به آدرس تعیین شده توسط ثبات R)

![]()

![]()

در صورتی که فقط پیمایش یک جهته یک آرایه در حافظه بخش داده مدنظر باشد و از حافظه نهان داده استفاده گردد، کدام طراحی از بقیه بهتر است؟

حافظه نهان نگاشت مستقیم با اندازه بلوک بزرگ

حافظه نهانن تمامانجمنی با اندازه بلوک قابل قبول و معقول

حافظه نهان مجموعه انجمنی که اندازه تعداد راههای آن بیشتر باشد تا اندازه بلوک

حافظه نهان مجموعه انجمنی که اندازه بلوک بزرگتر داشته نسبت به اندازه تعداد راهها

فرض کنید پردازنده P دارای CPI=1/0، فرکانس کاری 1/5GHz باشد. ما میخواهیم یک معماری جدید برای پردازنده P طراحی کنیم، به گونهای که مدت زمان اجرای (execution time) برنامهها 30% کاهش یابد. اما تغییراتی که ما اعمال میکنیم، منجر به افزایش 20% در CPI پردازنده میشود. طراحی جدید پردازنده بایستی چند گیگاهرتز فرکانس کاری داشته باشد تا شرایط بالا را تأمین کند؟

1/84

2/23

2/56

3/18

فرض کنید یک حافظه نهان با معماری نگاشت مجموعه انجمنی (set associative) با دو خط (2-way) داشته باشید. مشخصات حافظه نهان، کدام مورد است؟

هر کلمه، 4 بایت است.

هر بلوک حافظه، 512 بایت است.

آدرسها به صورت بایت عرضه میشوند.

حافظه نهان، کلا دارای 1024 بلوک حافظه است.

یک پردازنده تکچرخه ای (single cycle) قادر است در هر 100 نانو ثانیه یک دستورالعمل را اجرا کند. این پردازنده میتواند به شکل ایدهآل به یک پردازنده خط لوله تبدیل شود، بهطوری که خط لوله پردازنده همیشه پر از دستورالعمل باشد. به هر حال، پردازنده جدید خط لوله دارای سربار زمانی یک نانو ثانیه برای ثباتهای بین مراحل است. خط لوله پردازنده مورد نظر باید دارای چند مرحله باشد تا بیشترین توان عملیاتی (throughput) را داشته باشد؟

5

9

10

1000

یک برنامه اسمبلی برای پردازنده MIPS، به شکل زیر نوشته شده است. در یک پردازنده خط لوله MIPS با 5 مرحله، چه مسیرهای ارسالی (forwarding paths) مورد نیاز است تا از مخاطره داده (data hazard) جلوگیری شود؟

loop;

addi R4,R4,4

addi R5,R5,4

Iw R6,0(R4)

sw R6,0(R5)

bne R4,R7

WB-EX,WB-MEM

WB-EX,MEM-EX

MEM-EX.WB-MEM

WB-EX,MEM-EX,WB-MEM

فرض کنید فرمت جدیدی برای نوشتن اعداد اعشاری به استاندارد IEEE-754 اضافه شده است که قسمت علامت همچنان 1 بیت، بخش توان دارای 9 بیت و بخش مانتیس دارای 15 بیت است. عدد 2/45 در این فرمت جدید، به چه شکل نشان داده میشود؟

s(1-bit) Exponent(9) Fraction(15)

0011111110011001100111000

0100000000001110011001100

0011111111011100110011000

0100000011011001100111000

در یک سیستم کامپیوتری، حافظه اصلی بایت است. حافظه مجازی 256 صفحه است و اندازه هر صفحه نیز بایت است. فضای آدرسدهی حافظه مجازی، چند بیت است؟

12

10

14

18

در یک سیستم کامپیوتری با حافظه مجازی، زمان دسترسی به حافظه اصلی 50 نانو ثانیه است. زمان انتقال یک بلاک از فضای مجازی به حافظه اصلی، برابر 10 میلی ثانیه است. با داشتن احتمال خطای صفحه برابر با ، زمان متوسط دسترسی به حافظه، اگر جدول صفحات در حافظه اصلی باشد، چند نانو ثانیه است؟

110

100

95

90