حل تشریحی سوالات معماری کامپیوتر پیشرفته - VLSI پیشرفته - کنکور دکتری مهندسی کامپیوتر 1403

سوالات معماری کامپیوتر پیشرفته - VLSI پیشرفته

25 سوالدر یک پردازنده که ولتاژ آن قابل کنترل است، کاهش 20 درصدی ولتاژ باعث کاهش 20 درصدی فرکانس کار پردازنده میشود. نسبت تقریبی توان مصرفی پردازنده با ولتاژ کاهش یافته بهتوان مصرفی آن در حالت عادی چقدر است؟

0/51

0/53

0/61

0/63

برای سرعت بخشیدن به عملیات ممیز شناور یک پردازنده گرافیکی برای اجرای یک برنامه خاص، دو راهکار پیشنهاد شده است:

الف- بهبود سختافزار برای اجرای 2 برابر سریعتر همه عملیات ممیز شناور

ب- بهبود سختافزار برای اجرای 20 برابر سریعتر دستور جذر ممیز شناور

در صورتی که همه دستورات ممیز شناور، 50 درصد و دستورات جذر ممیز شناور، 10 درصد زمان اجرای برنامه را شامل شوند، میزان تسریع اجرای برنامه برای حالتهای (الف) و (ب) بهترتیب کداماند؟

1/12 و 1/43

1/43 و 1/12

1/33 و 1/10

1/53 و 1/50

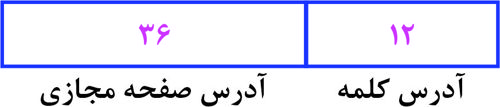

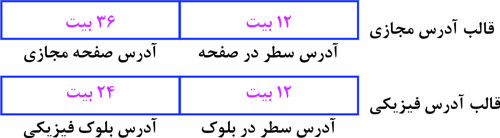

در یک پردازنده که دارای آدرس حافظه مجازی با قالب زیر است، آدرس حافظه فیزیکی 36 بیت دارد. برای ترجمه آدرس مجازی به فیزیکی، از دو بافر ترجمه TLB1 و TLB2 استفاده میشود. TLB1 دارای ظرفیت 128 درایه با نگاشت مستقیم و TLB2 با ظرفیت 512 درایه و با ساختار انجمنی 4 راهه (4 Way Set Associative) است. تعداد بیتهای مورد نیاز بهترتیب برای ساخت TLB1 و TLB2 کداماند؟

5760 و 23040

7808 و 31232

6748 و 27136

6912 و 27648

در یک پردازنده، قالب آدرس مجازی به شکل زیر است. حجم حافظه اصلی بایت و حجم حافظه مجازی بایت است. اگر حداکثر قطعه داشته باشیم و از یک بافر ترجمه TLB بهصورت تمام انجمنی (Fully Associative) استفاده کنیم، هر درایه TLB چند بیت است؟ (برای هر درایه یک بیت اعتبار در نظر بگیرید. اندازه صفحات و بلوکها 4KB است).

34

35

36

37

در یک سلسه مراتب حافظه، حافظههای نهان سطح یک، سطح دو و حافظه اصلی را داریم. با داشتن اطلاعات زیر، متوسط زمان دستیابی به حافظه کدام است؟

hit time L1=1ns

hit time L2=5ns

miss rate L1=15%

miss rate L2=10%

miss penalty L2=60CLK

2/2

2/3

2/4

2/5

در یک پردازنده دارای حافظه مجازی، آدرس دهی حافظه نهان بهصورت ایندکس فیزیکی و نشانه مجازی (Physically Indexed, Virtually Tagged) انجام میشود. اگر قالب آدرس مجازی و فیزیکی بهصورت زیر باشد، حجم حافظه نهان که بهصورت انجمنی 4 راهه (4Way Set Associative) است، چند کیلوبایت (KB) است؟

4

8

12

16

در یک پیشبینی کننده انشعاب دوسطحی از نوع (m,n)، در صورتی که بافر انشعاب با 10 بیت پایین PC ایندکس شود، تعداد بیت مورد نیاز برای پیادهسازی این بافر کدام است؟

اگر از شمارنده دوبیتی اشباع شونده برای پیشبینی انشعاب یک دستورالعمل انشعاب شرطی استفاده کنیم و الگوی پرشهای این دستور (از چپ به راست) بهصورت زیر باشد، چه نسبتی از پرشها درست پیشبینی شده است؟ (فرض کنید شمارنده در ابتدا مقدار را دارد.)

N,N,T,T,T,T,T,N,N,T,T,N,T,T,T,

در الگوریتم زمانبندی اجرای پویا و خارج از ترتیب (OOO) توماسولو، کدامیک از جملات زیر نادرست است؟

به ازای هر ایستگاه رزرو (Reservation station) یک واحد عملیاتی وجود دارد.

دستورالعملها از واحد دستورالعمل بهصورت اولین ورودی - اولین خروجی (FIFO)، وارد صف دستورالعمل میشوند.

تمام نتایج تولید شده توسط واحدهای عملیاتی و واحد بارگیری (Load unit)، روی یک گذرگاه داده مشترک قرار میگیرند.

هر ایستگاه رزرو، شامل اطلاعاتی دربارۀ عملی که باید انجام شود، اپرندها و اطلاعاتی راجع به چگونگی حل و فصل مخاطرات (Hazard) هستند.

در الگوریتم زمانبندی اجرای پویا و خارج از ترتیب (OOO) توماسولو که در آن اجرای دستورات میتواند با گمانهزنی (Speculative) باشد، کدامیک از عبارتهای زیر نادرست است؟

ورود دستورات بهترتیب برنامه، اجرای آنها خارج از ترتیب و اتمام آنها بهترتیب است.

با افزودن ROB به الگوریتم توماسولو، بافر ذخیرهسازی (Store Buffer) حذف شده و ROB کار آن را انجام میدهد.

با افزودن ROB ، تعداد از واحدهای عملیاتی ساده مثل INC و DEC حذف شده و ROB کار آن را انجام میدهد.

نیاز به یک بافر ROB، داریم که فاز اتمام دستورات (Commit) را متناسب با ترتیب ورود دستورات انجام دهد.

فرض کنید برای اجرای یک برنامه در یک سیستم با 100 پردازنده میخواهیم تسریع 50 برابری نسبت به اجرای همان برنامه با فقط یک پردازنده داشته باشیم. چند درصد برنامه باید قابلیت اجرای موازی داشته باشد؟

96/43

97/02

98/86

98/98

در یک سیستم چندپردازندهای با حافظه اصلی توزیعشده بین پردازندهها، هزینه دسترسی به حافظه دور توسط یک پردازنده 300ns است. اگر برای اجرای یک برنامه در این سیستم، 0/2 درصد از دسترسیهای به حافظه، مربوط به حافظۀ دور باشد، تعیین کنید اجرای برنامه در این حالت چند برابر نسبت به حالتی که همه دسترسیهای حافظه در حافظه محلی تأمین شود، کندتر است؟ (CPI را برای حالت بدون دسترسی به حافظه دور، 0/5 فرض کنید. فرکانس ساعت سیستم 2GHZ است.)

1/5

1/6

1/7

1/83

در سیستمهای چند پردازندهای که از حافظه مشترک استفاده میکنند، همسانی حافظه نهان (Cache Coherency) یکی از چالشهای مهم است. کدامیک از عبارتهای زیر در این زمینه، نادرست است؟

پروتکل همسانی Snoopy، معمولاً برای سیستمهای چند پردازنده با حافظه مشترک توزیع نشده (SMP) و پروتکل Directory، برای سیستمهای چند پردازنده با حافظه مشترک توزیع شده استفاده میشوند.

در پروتکل Snoopy، اگر یکی از حافظههای نهان بلوکی را بهصورت Modified در اختیار داشته باشد، با دریافت پیام Write miss، بلوک خود را در حافظه مینویسد و به حالت Invalid میرود.

در پروتکل Snoopy، اگر یکی از حافظههای نهان، بلوکی را بهصورت Shared در اختیار داشته باشد، با دریافت پیام Write miss از گذرگاه، آن بلوک را Invalid میکند.

در پروتکل Snoopy، اگر یکی از حافظه نهان، بلوکی را بهصورت Shared در اختیار داشته باشد و از سمت پردازنده خود پیام Write miss دریافت کند، بلوک را در اختیار پردازنده قرار داده و آن را به حالت Modified درمیآورد.

در یک سیستم دوپردازندهای با حافظه مشترک، بلوکهای حافظه نهان مربوط به هر یک از پردازندهها 2 کلمهای هستند. اگر دو کلمه A و B که در یک بلوک حافظۀ اصلی هستند، توسط این دو پردازنده بهترتیب زیر مورد دسترسی قرار گیرند، تعیینن کنید کدامیک "دسترسی اشتراکی درست" (True sharing miss) و کدامیک "دسترسی اشتراکی غلط" (False Sharing miss) هستند؟ (برای شروع فرض میشود بلوک مورد نظر بهصورت Modified در اختیار P2 است و P1 قبلاً دسترسی به این بلوک نداشته است.)

1:P1 Writes A

2:P2 Writes B

2:P1 Writes B

1:P2 Writes A

صحیح، غلط، صحیح، غلط

غلط، صحیح، غلط، صحیح

صحیح، صحیح، غلط، غلط

غلط، غلط، صحیح، صحیح

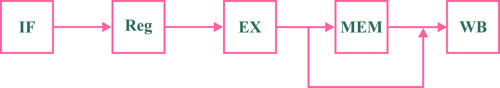

در خط لوله 5 قسمتی پردازنده MIPS، 4 دستورالعمل زیر بهترتیب وارد خط لوله میشوند. اگر فقط واحد Forwarding داشته باشیم، برای جلوگیری از مخاطرات در خط لوله چند دستور NOP و در کجای برنامه اضافه کنیم؟

(توجه: در نیمه اول CLK، نتایج در بانک ثبات نوشته و در نیمه دوم CLK، ثباتها خوانده میشوند.)

یک دستور NOP بین و

دو دستور NOP: یکی بین و و یکی بین و

سه دستور NOP: که هر یک بین و ، و ، و

با داشتن Forwarding برای این دستورات، نیاز به NOP نیست.

مقدار تلاش منطقی (g) هر کدام از ورودیها مدار زیر، چقدر است؟

g=(3+r)/(3)

g=(3r)/(1+r)

g=(3+r)/(1+r)

g=(3+r)/(1+r/3)

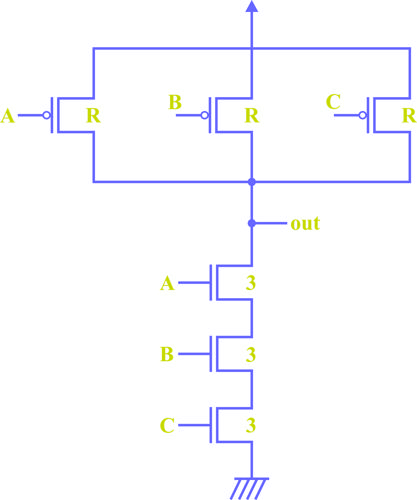

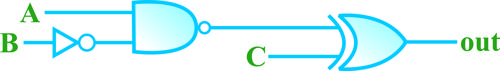

مقدار ضریب تغییرات گره خروجی out در مدار زیر چقدر است؟ (فرض کنید احتمال یک بودن ورودیهای A و B، برابر با و احتمال یک بودن ورودی C، برابر با است.)

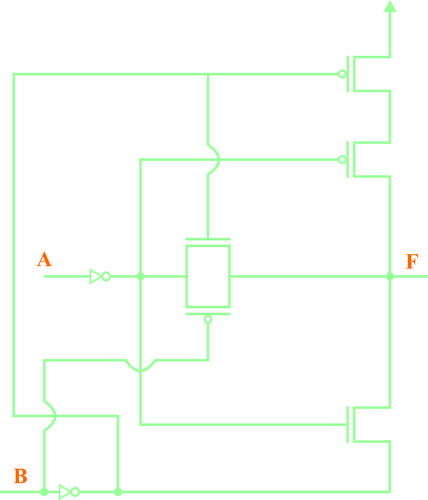

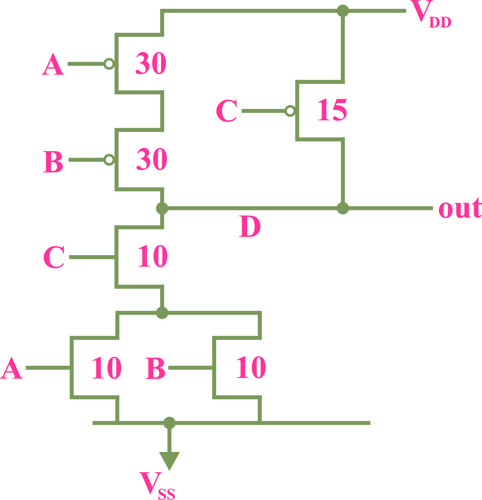

مدار زیر چه تابعی را پیاده میکند؟

F=A AND B

F=A NOR B

F=A XOR B

F=A XNOR B

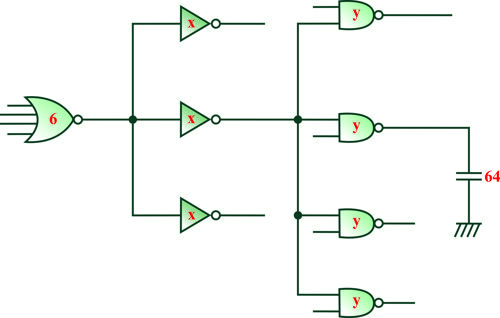

اگر نسبت اندازه ترانزیستورها در معکوس کننده واحد برابر با دو به یک باشد، مقدار بهینه تأخیر تلاش منطقی هر مرحله در مدار زیر به کدام مورد نزدیک است؟

f=6

f=7

f=8

f=9

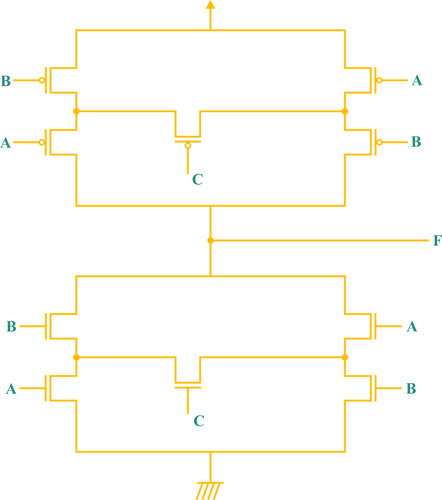

مدار زیر چه تابعی را پیاده میکند؟

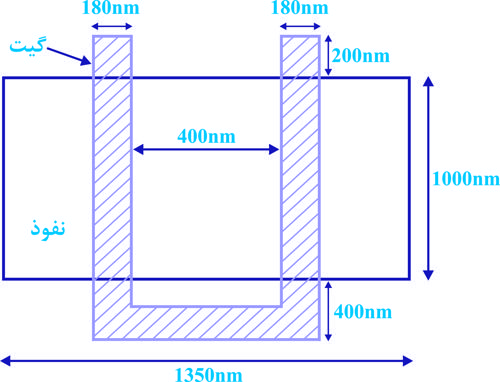

اگر مقدار خازن گیت در واحد سطح برابر با باشد، مقدار کل خازن گیت در شکل زیر چقدر است؟

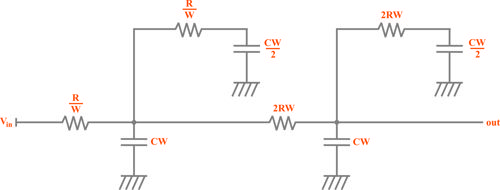

مقدار تأخیر مدار زیر از تا خروجی Out با استفاده از مدل تأخیر المور، کدام است؟

در مدار زیر چنانچه ورودیهای A و C بتوانید به جای یکدیگر سوئیچ زده شوند، ممکن است به اشتباه مقادیر درستی را در خروجی داشته باشیم و به همین دلیل نتوانیم خطائی را شناسایی کنیم. کدام بردارهای آزمون (در هر دو بخش nMOS و pMOS) قادر به شناسایی چنین خطایی است؟

ABC=000

ABC=011

ABC=011

ABC=110

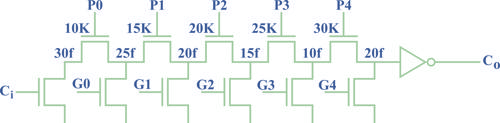

در شکل زیر و است. اگر تأخیر وارونگر 100psec باشد، تأخیر مدار چقدر خواهد شد؟

2.35ns

2.43ns

2250psec

2500psec

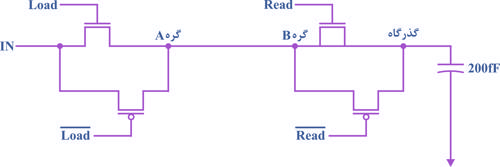

شکل زیر یک لچ پویا (عنصر ذخیره داده) را با یک پورت دستیابی که خروجی لچ را به گذرگاه متصل کرده است. نشان میدهد. چنانچه لچ مقدار صفر را ذخیره کرده (در گره A) و گذرگاه در آغاز LOW باشد، هنگامی که سیگنال Read را فعال کنیم، چه اتفاقی میافتد؟

مشکلی وجود ندارد.

مشکل اشتراک بار وجود دارد و مقدار گره A تغییر میکند.

اگر گیت انتقالی Read بزرگتر باشد، مشکلی پیش نخواهد آمد.

مشکل اشتراک بار وجود دارد، اما مقدار گره A تغییر پیدا نمیکند.