حل تشریحی سوالات الکترونیک دیجیتال - کنکور ارشد مهندسی کامپیوتر 1402

منوی آزمون (درس ها)

سوالات الکترونیک دیجیتال

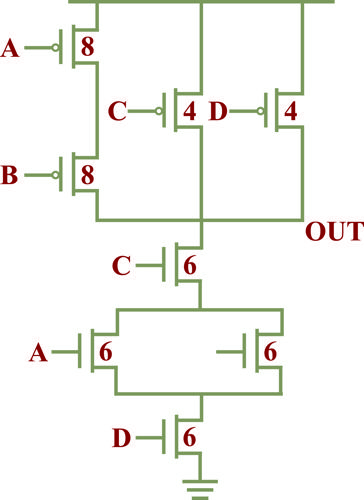

6 سوالپیاده سازی تابع در CMOS ایستا را در نظر بگیرید. مدل کانال بلند را برای ترانزیستورها فرض کنید. انداره ترانزیستورها را به گونهای تعیین میکنیم که مقاومت درایوکنندگی این گیت با یک وارونگر با مشخصات Wn/L=2 و Wp/L=4 یکسان باشد. در صورتی که W/L ترانزیستور pMOS دارای ورودی D برابر4 باشد، W/L ترانزیستور nMOS دارای ورودی A، کدام است؟

6

8

پردازندهای را در فرایند 0/18 میکرومتر با ولتاژ منبع تغذیه 1/2 ولت در نظر بگیرید. مساحت این پردازنده برابر 0/8 میلی متر مربع است. اگر فرایند به 90 نانومتر با ولتاژ منبع تغذیه 1 ولت تغییر مقیاس یابد، مساحت چند میلی متر مربع خواهد بود؟

0/2

0/32

0/4

1/6

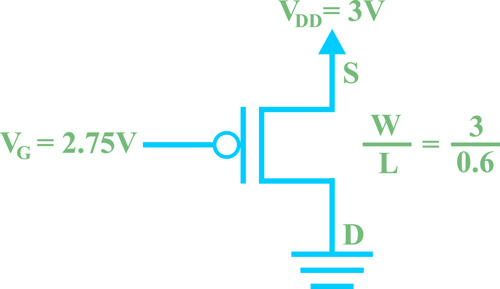

ترانزیستور شکل زیر در چه ناحیهای کار میکند و جریان کدام است؟ (از مدولاسیون طول کانال و جریان های نشتی صرف نظر کنید.) ,, 0/5V

خطی و 7/5

اشباع و 6/75

اشباع و 12/5

قطع و

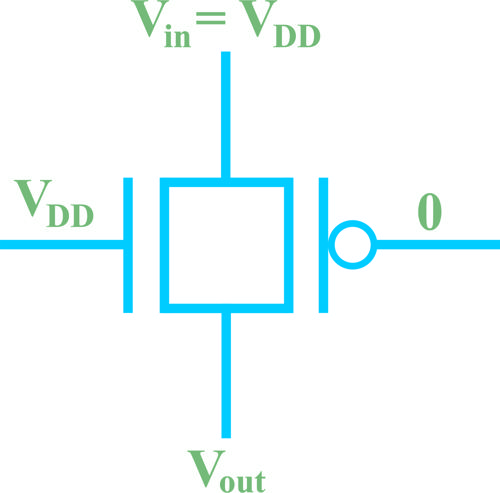

کدام جمله درمورد خروجی یک گیت عبور به شکل زیر درست است؟ (فرض کنید )

ترانزیستور NMOS ولتاژ روی خروجی قرار میدهد و ترانزیستور PMOS ولتاژ روی خروجی میگذارد، لذا بین این دو ترانزیستور رقابت رخ میدهد و ولتاژ خروجی بین دو مقدار و خواهد بود

ترانزیستور NMOS پس از شارژ خروجی تا ولتاژ خاموش میشود. ترانزیستور PMOS ولتاژ روی خروجی قرار میدهد، لذا بدون رخ دادن هیچ رقابتی، خروجی برابر خواهد شد.

هر دو ترانزیستور ولتاژ روی خروجی قرار میدهند، لذا خروجی برابر خواهد شد.

هر دو ترانزیستور ولتاژ روی خروجی قرار میدهند، لذا خروجی برابر خواهد شد.

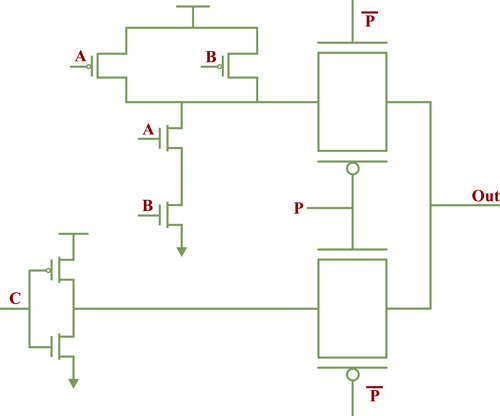

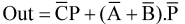

مدار زیر چه تابعی را پیاده سازی میکند؟

تاخیر انتشار یک وارونگر، که میانگین تاخیر نزول و صعود است، 0.72 نانوثانیه است. فرض کنید، جریان شارژ خازن خروجی نصف جریان دشارژ (تخلیه) ان باشد. اگر به علت اضافه کردن یکبار خارجی 1 پیکوفارد به خروجی وارونگر، تاخیر انتشار آن 70% افزایش یابد، خازن معادل خروجی وارونگر چند پیکوفاراد خواهد بود؟

0/7

1/43

2/4

2/7