حل تشریحی سوالات معماری کامپیوتر پیشرفته - VLSI پیشرفته - کنکور دکتری مهندسی کامپیوتر 1404

سوالات معماری کامپیوتر پیشرفته - VLSI پیشرفته

25 سوالکدام یک از موارد زیر، از مزایای روش (Interleaved Memory) به نسبت راه کارهایی که از این روش استفاده نمی کنند نیست؟

کاهش CPI پردازنده ها

کاهش سربار پیاده سازی حافظه ها

افزایش Concurrency (همروندی) در اجرای برنامه ها

افزایش سرعت دسترسی به Chip تراشه های حافظه اصلی به دلیل حجم کوچک تر Chipها

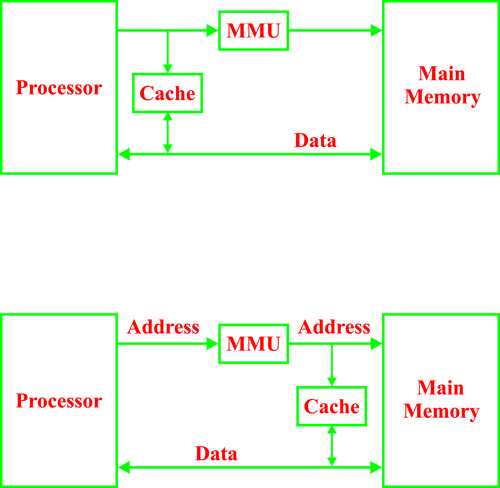

دو معماری کامپیوتر زیر را در نظر بگیرید. کدام مورد در خصوص نحوه آدرس دهی حافظه نهان معماری "الف" و "ب" به ترتیب درست است؟ (راهنمایی: هر دو معماری از آدرس دهی Vityual استفاده می کنند.)

logical و logical

physical و logical

physical و physical

logical و physical

با در نظر گرفتن سربار پیاده سازی سیاست های نوشتن Write through و Write back، کدام سیاست برای پیاده سازی L1 Instruction Cache پیشنهاد می شود؟

Write Back با حذف فیلد Dirty یا Use

تفاوتی بین آنها از نظر سربار پیاده سازی نیست.

Write Back

Write through

تحت چه شرایطی (Clock Cycle Per Instruction)CPI می تواند کوچکتر از 1 باشد؟

با تغییر ساختار حافظه پنهان

زمانی که در خط لوله هیچ گونه هزاردی نداشته باشیم.

زمانی که تعدادی از دستورات بتوانند به صورت موازی اجرا شوند.

در حالت ایدآل، مقدار CPI می تواند 1 باشد و کمتر از 1 امکان پذیر نیست.

یکی از راه های کاهش نرخ شکست (Miss Rate) در طراحی حافظه نهان، افزایش ظرفیت حافظه نهان می باشد. کدام یک از موارد زیر، از معایب این روش است؟

افزایش زمان Hit Time

افزایش Miss Penalty

افزایش Miss Time

افزایش CPI

در یک پردازنده 2-issue superscalar از تکنیک loop unrolling برای حذف / کاهش تأخیر ناشی از وابستگی های داده ای استفاده می شود. پردازنده امکان اجرای موازی یک دستور ممیز شناور را به همراه هر دستور از نوع دیگری (غیر از ممیز شناور) مثل مراجعه به حافظه و یا محاسبات اعداد صحیح دارد. جدول زیر، میزان تأخی آماده سازی نتایج در اجرای متوالی دستورات را در واحد پالس ساعت نشان می دهد. اگر فرض کنیم که برای اجرای دستورات حلقه زیر از دوبار باز کردن حلقه (unrolling=2) استفاده شود، تعداد پالس های ساعت مورد نیاز برای اجرای تکه کد زیر چقدر است؟

(دستورات بررسی شرط و پرش شرطی، هر کدام یک پالس ساعت تأخیر نیاز دارند.

تأخیر | نوع دستور بعدی | نوع دستور در حالِ اجرا |

|---|---|---|

3 | ممیز شناور | ممیز شناور |

2 | نوشتن در حافظه | ممیز شناور |

1 | ممیز شناور | خواندن از حافظه |

0 | نوشتن در حافظه | خواندن از حافظه |

0 | محاسبات صحیح | محاسبات صحیح |

Loop:L.D F0,0 ;F0=array element

ADD.D F4,F0,F2 ;floating point add

S.D 0(R1),F4 ;store result

SUBI R1,R1.#8 ;decrement pointer

BNEZ R1,Loop ;branch

11

10

9

8

در حافظه نهان با ثابت نگه داشتن ظرفیت کل آن (total cache size)، اندازه بلاک ها را افزایش داده ایم. کدام مورد در خصوص انواع نرخ نبود داده (cach miss) اعم از Compulsory و Capacity درست است؟

موجب کاهش نرخ نبودِ داده از نوع conflict می شود.

موجب افزایش نرخ نبودِ داده از نوع conflict می شود.

موجب ثابت ماندن نرخ نبودِ داده از نوع conflict می شود.

به طور موقت، باعث کاهش نرخ نبود داده از نوع Compulsory می شود.

در رویکرد پیش بینی انشعاب (Dynamic branch predictin)، روش پیش بینی انشعاب دوبیتی (2-bit predictor) در حلقه تودرتوی زیر، چند بار پیش بینی نادرست دارد؟ (فرض کنید اولین پیش بینی درست باشد.)

200

201

202

20000

در یک پردازنده با خط لوله 5 مرحله ای و قابلیت پیش بینی انشعاب، برنامه ای در حال اجرا است که 20 درصد دستورات آن، انشعاب هستند. فرض کنید Clock Per Instruction (CPI) در حالت ایده آل برابر 1/2 باشد. اگر دقت پیش بینی انشعاب 80 درصد باشد و هر پیش بینی اشتباه 4 چرخه ساعت هزینه زمانی داشته باشد، میزان CPI چه مقدار خواهد بود؟

1/36

2

2/24

4/4

در پردازنده ای با معماری 32 بیتی، میزان حافظه نهان 8KB است و با تکنیک Direct map پیاده سازی شده. اندازه هر بلاک حافظه نهان 4 کلمه و هر کلمه 4 بایت است. برای جستجوی داده در این حافظه، پهنای مقایسه گری که داده مورد نظر CPU را با داده موجود در حافظه بررسی می کند، چند بیت است؟

32

20

19

9

کاربرد الگوریتم توماسلو (Tomasulo) چیست؟

کاهش هزاردهای ساختاری

کاهش هزاردهای وابستگی داده ها

کاهش هزاردهای کنترلی

موارد 2 و 3

پردازنده ای دارای ساختار خط لوله است. 4 ایستگاه اول باید طی شود تا آدرس دستورات پرش محاسبه شود. بعد از آن 2 ایستگاه دیگر طی شود تا صحت شرط مشخص شود. اگر استراتژی برخورد با دستورات پرش، فرض بر taken بودن باشد ولی دستوری که وارد شده not taken باشد، آنگاه تعداد تأخیر (stall) برای این شرایط، چند پالس ساعت می شود؟

6

5

3

1

وقتی از cache استفاده می شود، برای کاهش زمان دسترسی به حافظه می توان از روش critical word first استفاده کرد یعنی وقتی که miss رخ می دهد ابتدا کلمه مورد نظر CPU و سپس بقیه کلمات بلوک را بخواند. این استراتژی باعث بهبود چه موردی می شود؟

کاهش miss rate

کاهش hit time

کاهش miss penalty

کاهش hit time و افزایش miss penalty

در یک پردازنده با 4 هسته پردازشی و فرکانس کاری 2GHz، 10 درصد دستورات در هسته ها نیاز به ارتباط با سایر هسته ها دارند و به ازای آن دستورات، عملیات هسته مربوط تا اجابت درخواست به مدت 2 نانوثانیه متوقف می شود. اگر CPI در پردازنده در حالتی که به ارتباط بین هسته ها نیاز نباشد، برابر 0/3 درصد دستورات آن نیاز به ارتباط دارند و زمان انتظار پردازنده در هر ارتباط 3 نانو ثانیه است، به چه میزان است؟

3

2/4

2

1/5

در سیستم چندپردازنده (Multiprocessors) برای همگن بودن حافظه های نهان همه پردازنده ها (cache coherence) از روش بشنود (Snooping) استفاده می شود. اگر یک بلوک از حافظه در حافظه نهان چند پردازنده مختلف باشد و یکی از آن پردازنده ها بخواهد که محتویات بلوک مذکور را تغییر دهد، چه وقایعی رخ می دهد؟

پردازنده نویسنده، بلوک را exclusive می برد و بقیه پردازنده ها بلوک را shared می کنند.

پردازنده نویسنده، بلوک را به حالت invalid می برد و بقیه پردازنده ها بلوک را exclusive می کنند.

پردازنده نویسنده، بلوک را به حالت shared می برد و بقیه پردازنده ها بلوک را invalid می کنند.

پردازنده نویسنده، بلوک را به حالت exclusive می برد و بقیه پردازنده ها بلوک را invalid می کنند.

کدام مورد، در خصوص عواقب ناشی از عدم رعایت قواعد طراحی درست نیست؟

افزایش تعداد متوسط تراشه های خراب در مرحله ساخت

معمولا، کاهش طول عمر تراشه

خراب شدن تابع منطقی طرح

افزایش احتمالی تأخیر طرح

کدام مورد در خصوص قفل شدگی (Latchup) و اثر بدنه (Body effect) درست است؟

اثر بدنه وابسته به مقدار ولتاژ آستانه است و با تغییر ضخامت عایق زیر گیت می توان آن را از بین برد.

اثر بدنه با تغییر لی اوت یک گیت قابل رفع نیست ولی قفل شدگی را با تغییر رسم لی اوت می توان از بین برد.

هم اثر بدنه و هم قفل شدگی را با تغییر نوع فناوری ساخت می توان از بین برد.

هم اثر بدنه و هم قفل شدگی را با تغییر رسم لی اوت می توان از بین برد.

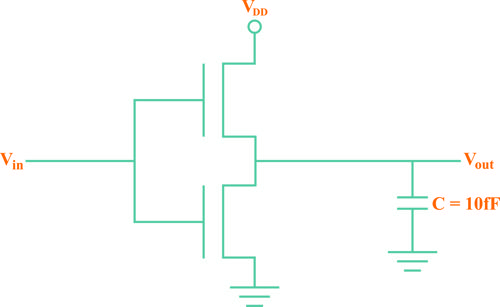

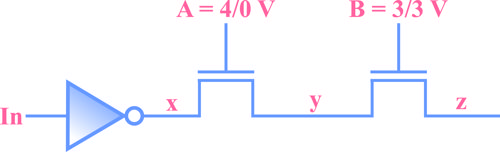

به ورودی وارونگر زیر، سیگنالی با پریود 10 نانو ثانیه و با ولتاژ 3/3 ولت متصل شده است. مقدار توان دینامیکی مصرف شده در این دروازه، به طور تقریبی کدام است؟

5mW

12mW

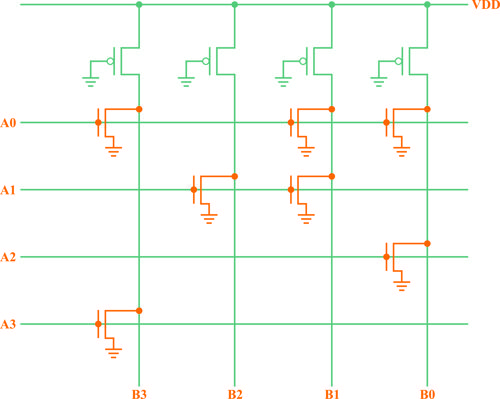

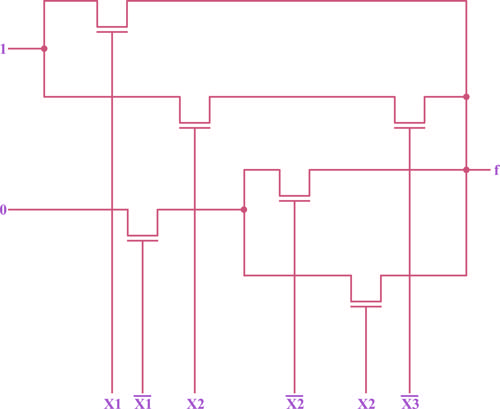

در حافظه فقط خواندنی زیر، بیت های بیت های آدرس و بیت های داده خروجی هستند. محتوای دو آدرس 0001 و 1010 به ترتیب کدام است؟

0011 و 0001

0100 و 1000

0100 و 0001

0010 و 1000

اگر تعداد ماسک های مورد نیاز برای ساخت یک ترانزیستور NMOS با یک لایه فلز در یک فناوری ساخت، برابر با 4 ماسک باشد، تعداد ماسک های لازم برای ساخت یک PMOS با 6 لایه فلز کدام است؟

15

10

9

8

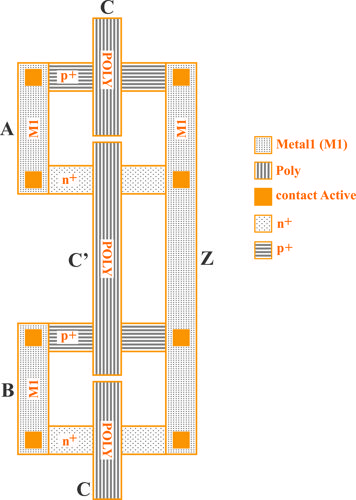

در لی اوت زیر، پورت های C، B، A و C=NOT(C) ورودی های مدار و Z خروجی آن است. این لی اوت (lay out) چه تابع منطقی را پیاده می کند؟

AND سه ورودی

MUX دو به یک

NOR سه ورودی

NAND سه ورودی

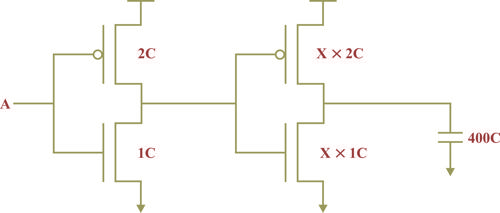

بافر دوطبقه زیر را در نظر بگیرید. بهترین اندازه برای طبقه دوم (x) برای اینکه تأخیر شارژ خازن خروجی حداقل شود، کدام است؟

20

14/1

11/5

10

شکل زیر، چه تابعی را پیاده سازی می کند؟

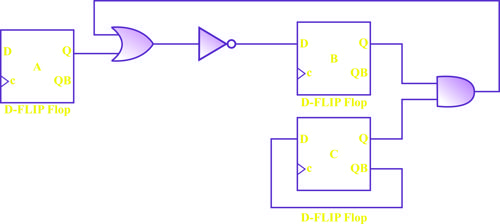

برای مدار زیر که تمام فلیپ فلاپ ها به پالس ساعت یکسان وصل هستند، اطلاعات زیر داده شده است. کوچک ترین پریود پالس ساعت که این مدار می تواند به درستی کار کند، برحسب نانوثانیه چقدر است؟

Setup time=5 nsec, 3 nsec<Clock-to-Q delay <4 nsec, 1 nsec<NOT gate delay<4 nsec, 2 nsec<AND gate delay<6 nsec, 2 nsec<OR gate delay<6 nsec

12

24

25

50

مدار شکل زیر، از یک معکوس کننده CMOS و دو ترانزیستور تشکیل شده و پارامترهای مدار به صورت Vdd=3,Vt=0.6V است.

اگر ورودی مدار صفر ولت باشد، ولتاژ نقاط Y و Z به ترتیب چند ولت است؟

3 و 2/7

3/4 و 2/7

3 و 3

2/4 و 1/8